Najczęściej używaną pamięcią masową w systemach retro jest karta CF, ze względu na prostotę i łatwość jej użycia w takich systemach. Wykorzystuje się do tego celu tryb „True IDE” karty i możliwość programowego przełączenia jej w tryb 8-bitowy, a od strony elektrycznej zgodność z bezpośrednim podłączeniem się do szyny procesora jak każdy inny układ IO. Pewna ilość modeli kart o pojemności 32-256MB umożliwia bezproblemową pracę z takim połączeniem, co jest powszechnie stosowane w amatorskich konstrukcjach jak i profesjonalnych (np. starsze modele routerów Cisco). Problemem są karty CF przygotowane na rynek konsumencki spełniające rygory standardu CF. Tu pojawia się niezgodność przebiegów czasowych typowego podłączenia do szyny Z80 z wymaganiami standardu CF.

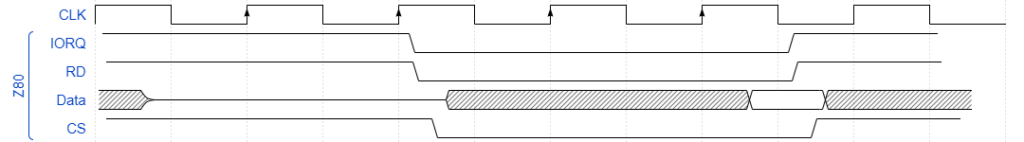

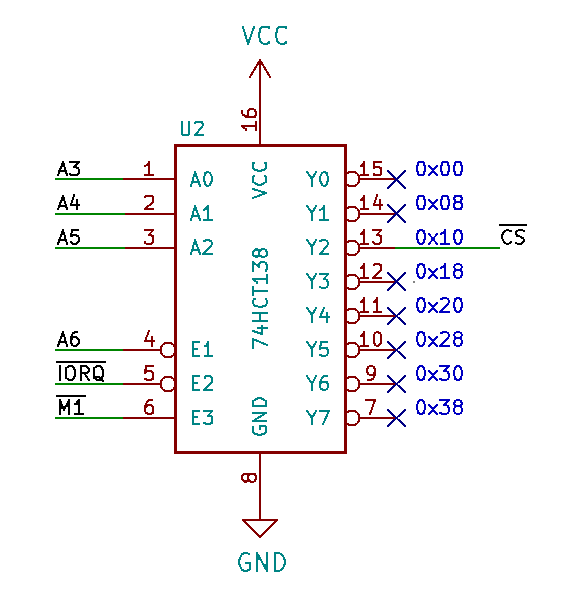

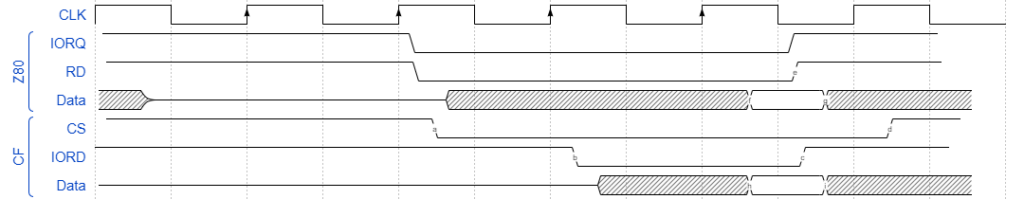

Jak widać z przebiegu czasowego, w Z80 sygnały /IORQ i /RD pojawiają się prawie jednocześnie, a powstały sygnał /CS sterujący kartą CF jest opóźniony przez czas propagacji sygnału /IORQ w dekoderze adresów, przez najczęściej do tego celu stosowany układ 74HCT138 (sygnał /M1 jest w celu zablokowania wyboru układu w tracie potwierdzenia przyjęcia przerwania, należy zwrócić uwagę, że tak zbudowany dekoder generuje również lustrzany sygnał przy aktywnej linii A7 – tu przykładowo 0x10 i 0x90).

Jak widać z przebiegu czasowego, w Z80 sygnały /IORQ i /RD pojawiają się prawie jednocześnie, a powstały sygnał /CS sterujący kartą CF jest opóźniony przez czas propagacji sygnału /IORQ w dekoderze adresów, przez najczęściej do tego celu stosowany układ 74HCT138 (sygnał /M1 jest w celu zablokowania wyboru układu w tracie potwierdzenia przyjęcia przerwania, należy zwrócić uwagę, że tak zbudowany dekoder generuje również lustrzany sygnał przy aktywnej linii A7 – tu przykładowo 0x10 i 0x90).

Wymagania stawiane przez standard CF dla uniwersalnych kart pracujących w trybie „True IDE” różnią się od typowego podłączenia urządzeń IO do szyny Z80. W celu zachowania pełnej kompatybilności z tym standardem należy dostosować przebiegi czasowe do wymagań dla tryb PIO 0.

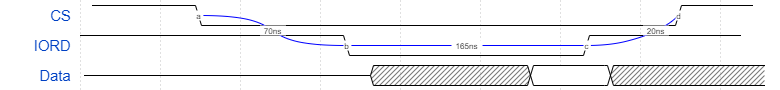

Po porównaniu tych przebiegów to możemy zauważyć, że rozpoczęcie cyklu odczytu znacząco się różni. W przypadku typowego podłączenia do szyny Z80 sygnał /CS pojawia się później (~10ns) niż sygnał /RD. Prawdopodobnie sekwencja /CS i późniejsze aktywowanie sygnału /RD jest wymagane na potrzeby wewnętrznych rejestrów odczytu karty CF. Opóźnienie to dla końcowego procesu odczytu jest korzystne, choć może być za małe do spełnienia wymagań. Najprostszym rozwiązaniem tego problemu jest zastosowanie filtru RC służącego do opóźnienia sygnału /RD co jest najczęściej stosowane w nowszych modułach CF RCBus [1],[2],[3]. Opóźnienie to, często nie jest wystarczające by spełniało wymagania uniwersalnych kart CF, lecz w przypadku przemysłowych kart poprawia ich działanie względem modułów które go nie posiadają. Spełnienie wymagań standardu CF rozwiązywane jest na dwa sposoby:

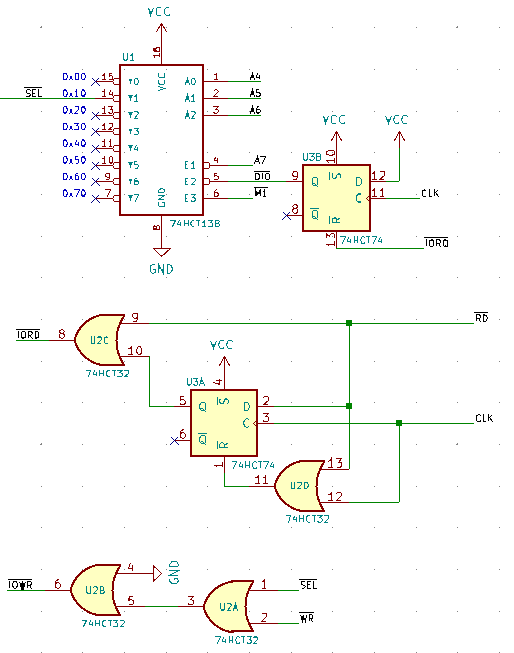

1. wcześniejsze generowanie sygnału /CS

2. opóźnienie pojawienia się sygnału /RD i /WR

W pierwszym przypadku wykorzystujemy cechę Z80, że na szynie adresowej ustalony adres pojawia się już w cyklu T1, który możemy wykorzystać do generowania sygnału /CS. Dzięki temu pojawienie się sygnału /RD (cykl T2) jest opóźnione w stosunku do wygenerowanego wcześniej /CS. Tu należy pamiętać, że sygnały sterujące kartą CF /IORD i /IOWR muszą zostać powiązane z sygnałem /IORQ procesora, gdyż dekoder adresu będzie aktywny po pojawieniu się każdego zgodnego adresu na szynie, w trakcie odwołań do pamięci i układów I/O. Zastosowane rozwiązanie zostało użyte w modułach [4],[5].

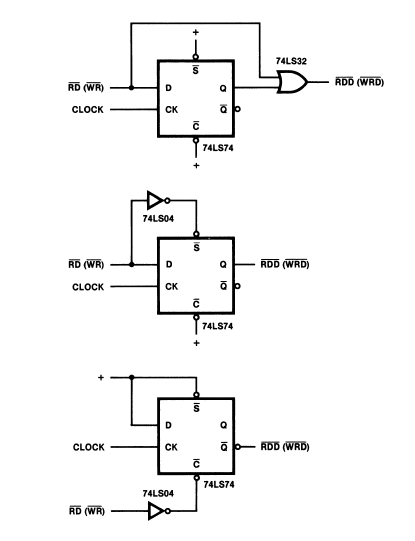

W przypadku opóźniania pojawienia się sygnałów /RD i /WR należy zastosować jeden z przedstawionych poniżej układów:

Przedstawione rozwiązanie jest często stosowane do dostosowania przebiegów Z80 do urządzeń peryferyjnych, które nie tolerują jednoczesnego pojawiania się sygnałów /IORQ i /RD (/WR) do ich sterowania (przykładowo układy z serii Z8500).

W moim najnowszym module CF zastosowałem drugą metodę, która jest najlepszym rozwiązaniem braku zgodności czasowych bezpośredniego podłączenia kart CF do szyny procesora Z80. Zastosowałem tam również układ wydłużający czas trwania sygnału /IORQ dla dekodera adresów, co poprawia końcowy cykl odczytu kart. Z przeprowadzonych doświadczeń wynikało, że sygnał /IOWR karty nie ma takich wymagań i zadowala się niewielkim opóźnieniem sygnału w stosunku do /CS.

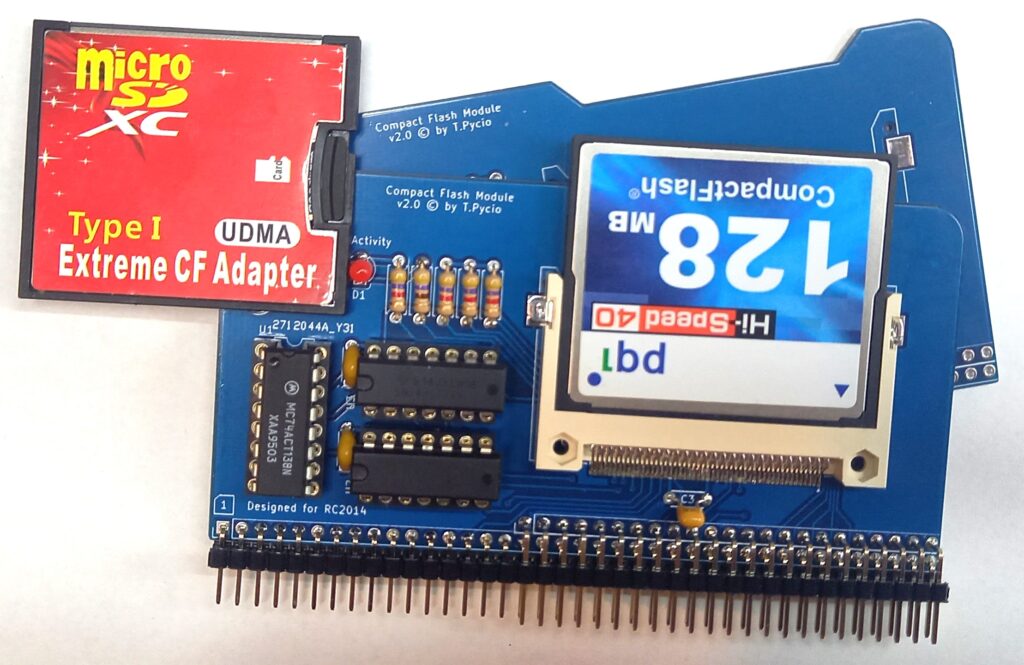

Tak przedstawiony układ zapewnia kompatybilność z większością dostępnych na rynku kart CF oraz adapterów SD do CF, które w pełni spełniają wymagania standardu CF

Najnowsza wersja modułu CF zawierająca kolejne usprawnienia jest dostępna na GitHub wraz z plikami produkcyjnym.