Twórca i właściciel marki RC2014 jasno określił że tylko jego moduły i zestawy mogą używać tej nazwy, co zdopingowało innych twórców modułów do uporządkowania i standaryzacji dodatkowych sygnałów jakie pojawiały się na tej szynie. Efektem tych prac jest wydanie pierwszej specyfikacji która definiuje rozmieszczenie i znaczenie poszczególnych pinów na złączach systemowych. Obecny format obejmuje różne architektury procesorów 8-bit, pozostałe, w tym 16-bitowe, powinny się pojawiać w kolejnych wydaniach specyfikacji RCBus. Przyjęta nazwa określa że łączy dotychczasowe modyfikacje jakie powstały na podstawie pierwowzoru (RC2014,BP80,RC80,RC40,…) i zachowuje z nimi kompatybilność.

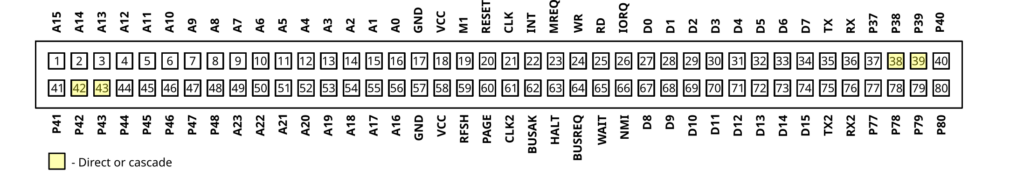

Jako podstawę przyjęto 80-pinowe złącze „goldpin” z rastrem 2,54mm znane już z rozwiązań stosowanych w RC80, BP80, umożliwiające używanie modułów 40-pinowych w części 1-40.

| Pin | Oznaczenie | Opis |

| 1-16 | A15-A0 | Szesnastobitowa szyna adresowa umożliwiająca zaadresowanie 64kB |

| 17 | GND | Masa zasilania |

| 18 | VCC | +5V |

| 19 | /M1 | Stan niski określa pobranie instrukcji dla rodziny procesorów Z80, dla pozostałych należy podciągnąć go do VCC w celu zachowania kompatybilności z modułami I/O |

| 20 | /RESET | Stan aktywny niski, reset systemu |

| 21 | CLK | Zegar systemowy (dla Z80 jest to standardowy 7,3728MHz) |

| 22 | /INT | Stan aktywny niski, OC, przerwanie |

| 23 | /MREQ | Stan aktywny niski, żądanie dostępu do pamięci |

| 24 | /WR | Stan aktywny niski, zapis do pamięci lub I/O |

| 25 | /RD | Stan aktywny niski, odczyt z pamięci lub I/O |

| 26 | /IORQ | Stan aktywny niski, żądanie dostępu do I/O |

| 27-34 | D0-D7 | Ośmiobitowa szyna danych |

| 35-36 | TX,RX | Sygnały portu szeregowego konsoli (Opcjonlane) |

| 37-48 | P37-P48 | Zarezerwowane sygnały używane wykorzystania przez specyficzne architektury. Pary pinów 38-39 oraz 42-43 mogą był łączone ze sobą bezpośrednio lub z przeplotem w danej parze. |

| 49-56 | A23-A16 | Dodatkowe linie szyny adresowej. Sygnały rozszerzające przestrzeń adresową do max. 8MB. (Opcjonalne, dozwolone jest niepełne odwzorowanie np. do linii A20) |

| 57 | GND | Masa zasilania |

| 58 | VCC | +5V |

| 59 | /RFSH | Stan aktywny niski. Sygnał odświeżania pamięci dynamicznej (Opcjonalne) |

| 60 | PAGE | Stan aktywny wysoki. Uaktywnienie pamięci RAM (całej lub określonej) stosowane do realizacji przełączników ROM/RAM, wydzielenia części pamięci przez inne moduły lub wyłączenia dostępu pamięci do szyny (Opcjonalne) |

| 61 | CLK2 | Dodatkowy zegar, stosowany do ustalania prędkości transmisji szeregowej (Opcjonalne) |

| 62 | /BUSAK | Stan aktywny niski. Potwierdzenie zwolnienia magistrali przez CPU. (Opcjonalne) |

| 63 | /HALT | Stan aktywny niski. Stan zatrzymania procesora. (Opcjonalne) |

| 64 | /BUSREQ | Stan aktywny niski, OC. Żądanie zwolnienia magistrali. (Opcjonalne) |

| 65 | /WAIT | Stan aktywny niski, OC. Żądanie wstawienia cyklów oczekiwania. (Opcjonalne) |

| 66 | /NMI | Stan aktywny niski, OC. Przerwanie niemaskowane. (Opcjonalne) |

| 67-74 | D8-D15 | Górna połówka szesnastobitowej szyny danych. |

| 75-76 | TX2,RX2 | Sygnały drugiego portu konsoli szeregowej (Opcjonalne, niepewne – może się zmienić ich znaczenie w przyszłych wydaniach) |

| 77-80 | P77-P80 | Zarezerwowane sygnały używane wykorzystania przez specyficzne architektury |

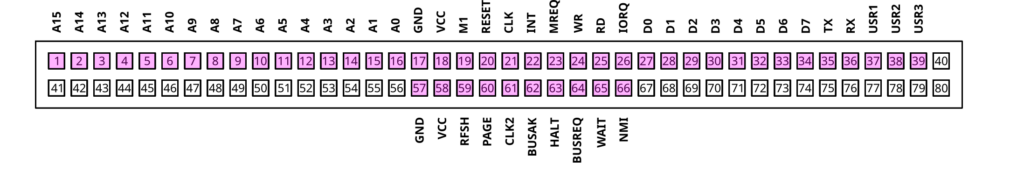

Standard RCBus zachowuje pełną kompatybilność ze standardem RC2014 i rozszerzonym RC2014:

Dla procesorów Z80, Z180 i Z280 w trybie 8-bit, w szynie RCBus pewna część z zarezerwowanych pinów została wykorzystana do realizacji wymogów tej architektury. Jak można zauważyć ten wariant jest całkowicie zgodny z przedstawionym wcześniej RC2014 i rozszerza go o brakujące tam sygnały umożliwiając realizację bardziej zaawansowanych konstrukcji.

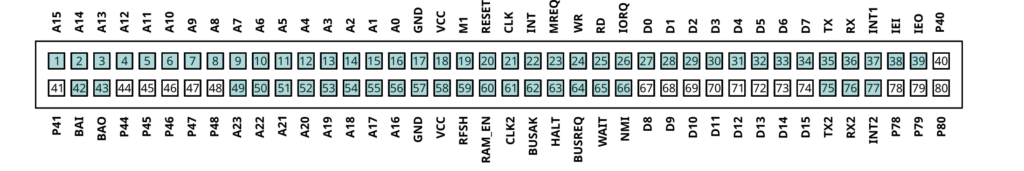

| Pin | Oznaczenie | Opis |

| 37 | /INT1 | Stan aktywny niski. Sygnał przerwania dla urządzeń nie obsługujących trybu wektorowych przerwań Zilog (Opcjonalne) |

| 38,39 | IEI,IEO | Kaskada priorytetów przerwań wektorowych. Na platerach do fizycznej realizacji używa się przeplotu tych pinów. (Opcjonalne) |

| 42,43 | BAI,BAO | Kaskada priorytetów arbitrażu dostępu do magistrali przez układy DMA, realizacja poprzez przeplot tych pinów na platerze. Urządzenie o najwyższym priorytecie musi zapewnić połączenie z sygnałem /BUSAK. (Opcjonalne) |

| 77 | /INT2 | Stan aktywny niski. Drugi sygnał przerwania dla urządzeń nie obsługujących trybu wektorowych przerwań Zilog (Opcjonalne) |

W obecnym standardzie brakuje sygnałów żądania obsługi DMA przez urządzenia zewnętrzne co zostało zawarte w agendzie do specyfikacji.

Opis pozostałych obsługiwanych architektur i dodatkowe informacje dołączę w tym miejscu w późniejszym czasie. Zależało mi by ten wpis pojawił się jak najszybciej.